6T-SRAM的构成和读写

MOSFET概要

金属氧化物半导体场效晶体管(简称:金氧半场效晶体管;英语:Metal-Oxide-Semiconductor Field-Effect Transistor,缩写:MOSFET),是一种可以广泛使用在模拟电路与数字电路的场效晶体管。金属氧化物半导体场效应管依照其沟道极性的不同,可分为电子占多数的N沟道型与空穴占多数的P沟道型,通常被称为N型金氧半场效晶体管(pMOSFET)与P型金氧半场效晶体管(pMOSFET)。

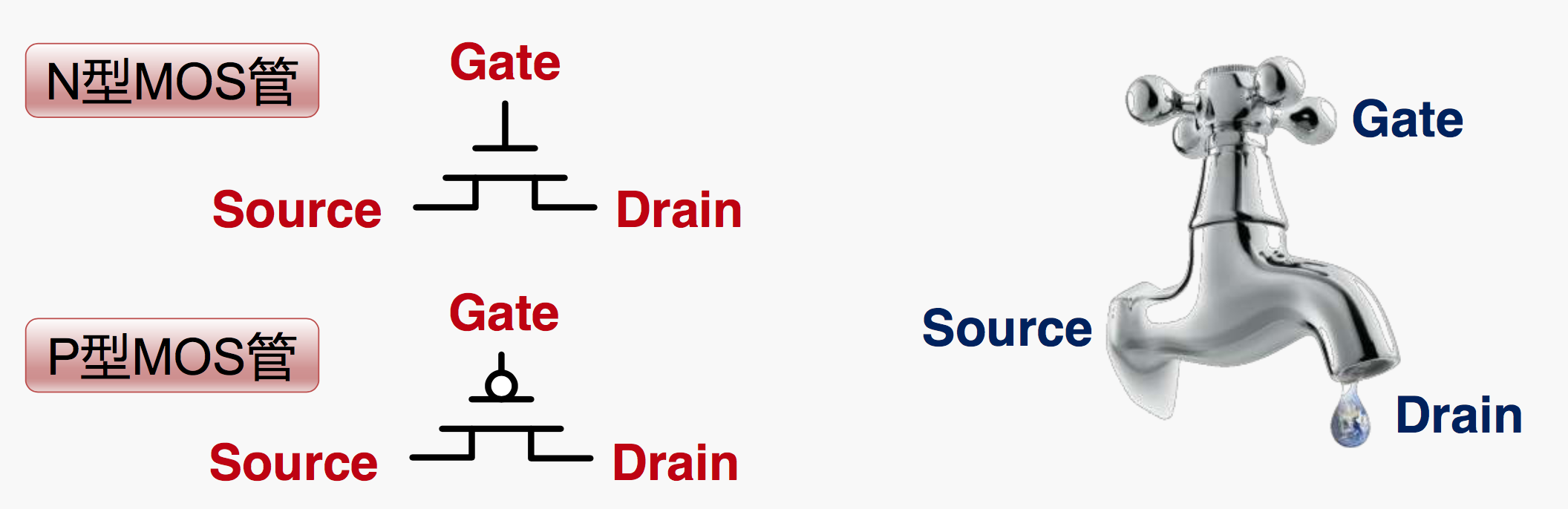

MOS管的电路符号有多种形式,最常见的设计是以一条垂直线代表沟道(Channel),两条和沟道平行的接线代表源极(Source)与漏极(Drain),左方和沟道垂直的接线代表栅极(Gate)。如下图所示:

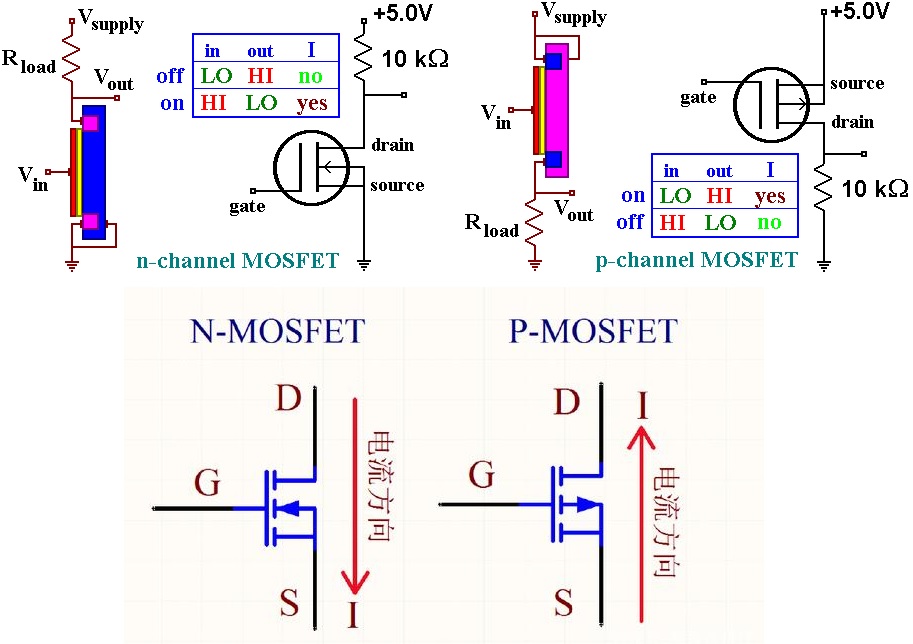

当栅极充电或设置为高电平时,nMOS晶体管允许电流流过;

当栅极放电或设置为低电平时,pMOS晶体管允许电流流过。

MOSFET极性、电路连接和电流方向如下图所示:

注:

- nMOS因Source一般接地(低电位),所以要让|VGS|>Vt,则Gate端一般要接正电压,这样管子才能导通;

- pMOS因Source端一般接VDD(高电平),所以要让|VGS|>Vt,则Gate端一般要接负电压(低与VDD的电压),这样管子才能导通。

逻辑门构成

互补式金属氧化物半导体(英语:Complementary Metal-Oxide-Semiconductor,缩写作 CMOS;简称互补式金氧半),是一种集成电路的设计工艺,可以在硅质晶圆模板上制出nMOS(n-type MOSFET)和pMOS(p-type MOSFET)的基本元件,由于nMOS与pMOS在物理特性上为互补性,因此被称为CMOS。此一般的工艺上,可用来制作电脑电器的静态随机存取内存、微控制器、微处理器与其他数字逻辑电路系统。

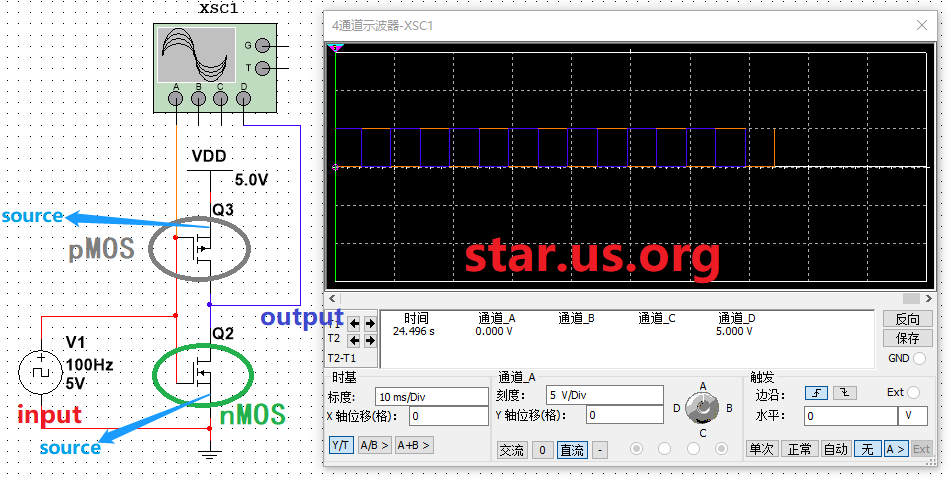

通过以互补的方式组合晶体管,可以开发出CMOS逻辑门。例如:在非门中,顶部是一个连接到电源线的pMOS晶体管,底部则是一个与地相连接的nMOS晶体管。pMOST晶体管用一个小圆圈表示与栅极相连。由于当输入关闭时pMOS晶体管导通,输入开启时nMOS晶体管导通,很容易就可以看出来,输出信号的状态总是与输入信号相反。

NI模拟可见输入(黄线)始终和输出(蓝线)取值相反。如下图所示:

6T SRAM构成

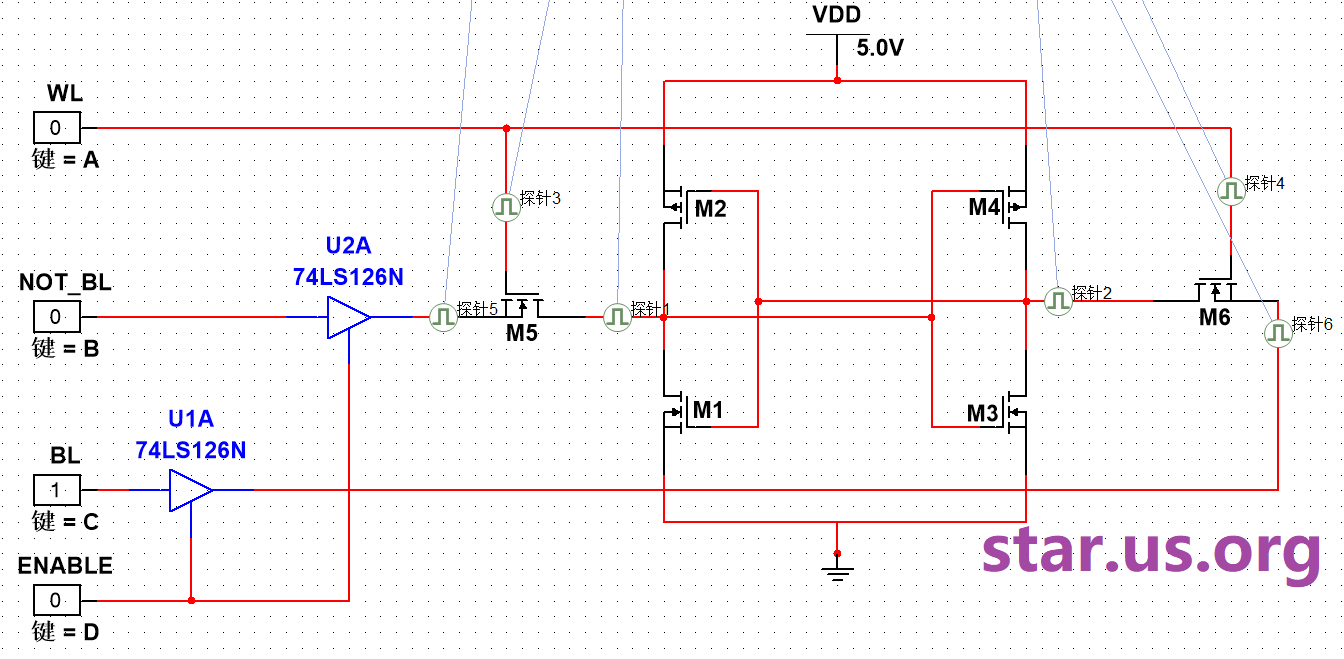

6T SRAM(Static Random Access Memory,静态随机存取存储器)电路如下图所示:

其中:

- WL是字线,用作传输控制信号,控制M5和M6的导通或截止。

- BL和NOT_BL(BL非)是位线,用作传送读写数据。

- M1,M2,M3,M4构成两个交叉耦合的反相器(即非门1的输出接非门2的输入,非门2的输出接非门1的输入)。这个结构只要保持通电就可以使得存入的1个bit的0或1始终保持稳定,由此体现出SRAM的Static。

- 探针1的位置:Q非端。

- 探针2的位置:Q端。

注:2个74LS126是额外加入方便控制两根位线用的3-STATE Buffer

6T SRAM写入

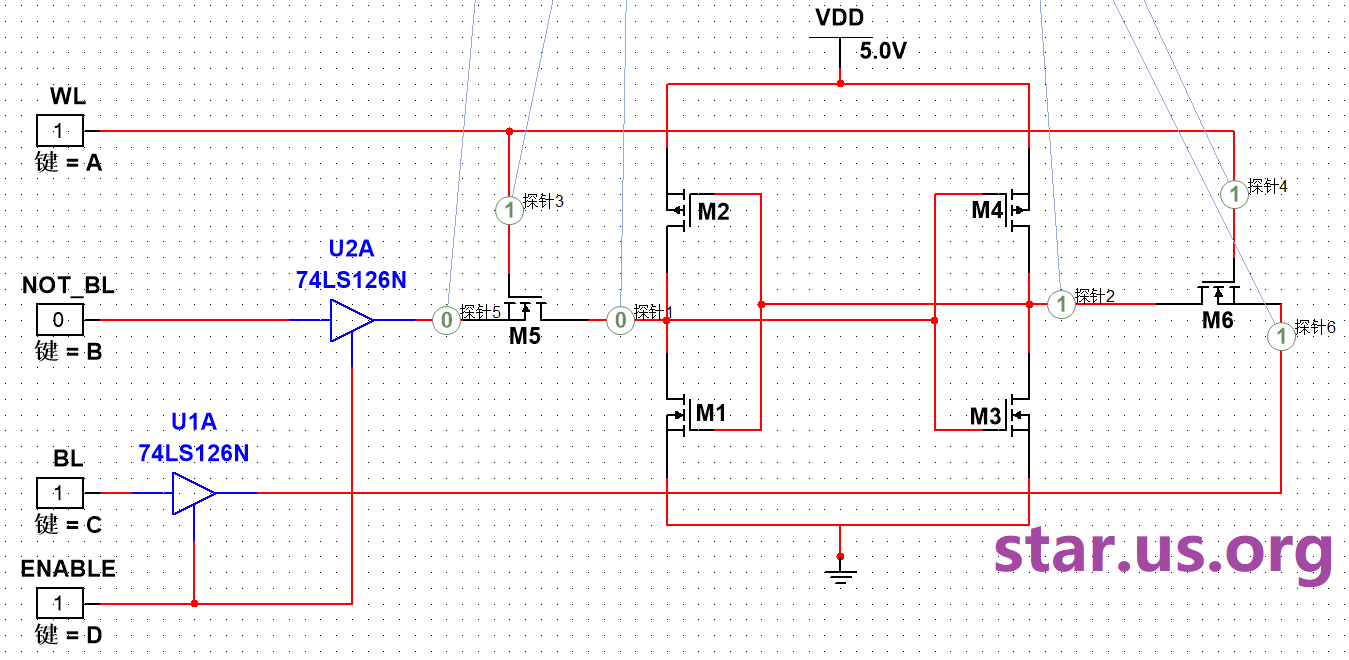

6T SRAM写入1,如下图所示:

写入过程简述:

- BL信号置1;NOT_BL信号置0。

- WL信号置1,使得M5和M6导通(nMOS的Gate端=1时导通)。

- ENABLE信号置1,两根位线上的0、1信号分别送达M5和M6。

BL上的信号1经过M6传递至Q端(探针2显示为1)和M1、M2的Gate端,使得M1导通(nMOS),M2截止(pMOS),所以Q非端的值取决于M1的输入,即从GND传导过来的值是0;与此同时NOT_BL上的信号0经过M5传递至Q非端也是0(探针1显示为0),Q非端上的0信号没有冲突,稳定保持0。

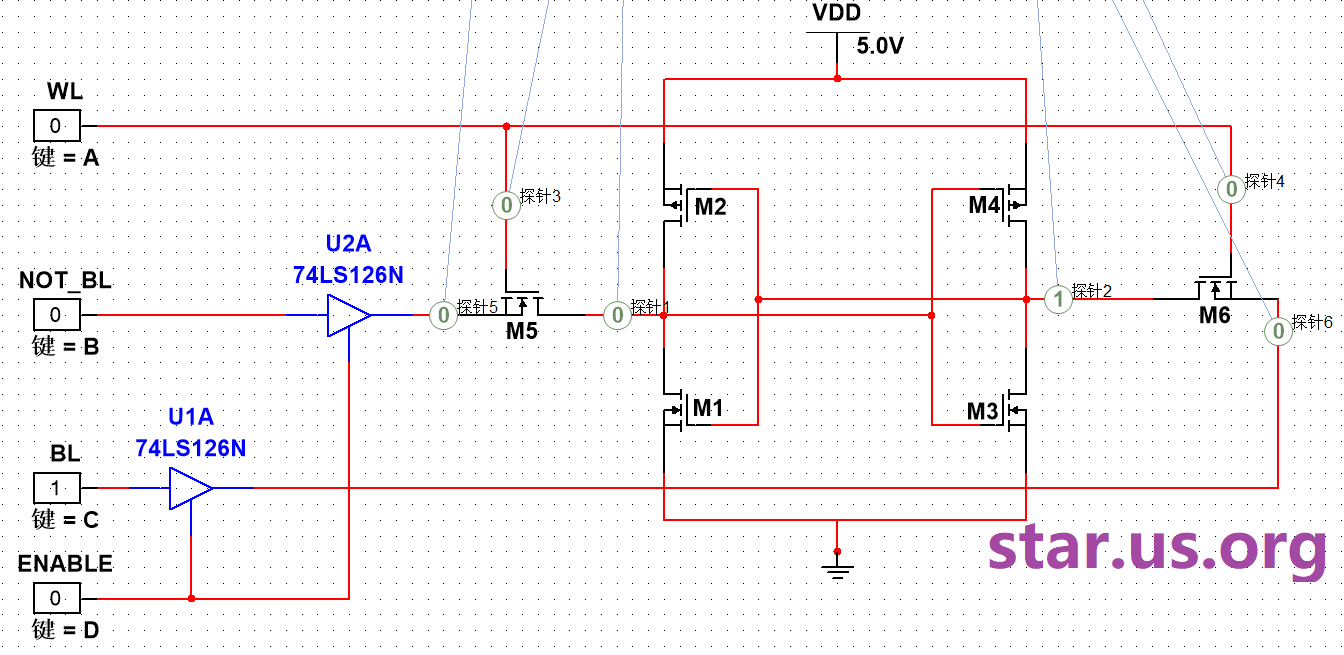

同理,NOT_BL上的信号0也传送到M3和M4的Gate端,使得M3截止(nMOS),M4导通(pMOS),所以Q端的值取决于M4的输入,即从VDD传入的值是1。与先前从BL传递进来的值无冲突,稳定保持1。 - 此时由外部驱动的输入信号使得SRAM达到稳定的状态。可将WL信号置0,ENABLE信号信号置0,关闭外部输入信号,如下图所示,SRAM稳定保持着写入的1。

对于写入操作来说,输入信号必须足够强,才能够覆盖原先的值!

6T SRAM读取

读取过程简述(假设之前已经写入1):

- WL信号置0,使M5和M6截止。

- 两根位线BL和NOT_BL都预充电至VDD(即数字1),并将ENABLE置1。

- WL信号置1,使M5和M6导通。

- 此时,由于M6处于导通状态,其Source端(BL)和Drain端(Q端)没有电压差,所以BL上的电压仍保持VDD。

同理,M5也处于导通状态,但是其Source端(NOT_BL)和Drain端(Q非端)存在电压差,会使电路放电,因此NOT_BL上的电压会下降。 - 两根位线BL和NOT_BL都会连接着Sense Amplifier(上图中没有画出),当它检测到NOT_BL上的电压降后,会输出1。

- 至此完成读出1的过程。

同样,如果Q端存的是0,则它和BL之间就会存在压差,导致放电,使BL上的电压下降。在被Sense AMP检测到后,输出0,从而完成读出0的过程。

补充说明 Sense Amplifier:

To sense the low power signals from a bitline that represents a data bit (1 or 0) stored in a memory cell, and amplify the small voltage swing to recognizable logic levels so the data can be interpreted properly by logic outside the memory

Conclusion

待续。。。

ref

- https://zh.wikipedia.org/wiki/%E9%87%91%E5%B1%AC%E6%B0%A7%E5%8C%96%E7%89%A9%E5%8D%8A%E5%B0%8E%E9%AB%94%E5%A0%B4%E6%95%88%E9%9B%BB%E6%99%B6%E9%AB%94

- https://zh.wikipedia.org/wiki/%E4%BA%92%E8%A3%9C%E5%BC%8F%E9%87%91%E5%B1%AC%E6%B0%A7%E5%8C%96%E7%89%A9%E5%8D%8A%E5%B0%8E%E9%AB%94

- http://www.physics.udel.edu/~watson/scen103/mos4.html

- http://www.physics.udel.edu/~watson/scen103/mos5.html

- https://xw.qq.com/partner/gdtadf/20190514A0BNIC/20190514A0BNIC00

- https://zhuanlan.zhihu.com/p/27260982

- http://www.elecfans.com/baike/bandaoti/bandaotiqijian/20100324205678.html

- https://www.youtube.com/watch?v=k5VBJcUcaWU

- http://web.engr.uky.edu/~elias/lectures/ln_16.pdf

- https://engineering.purdue.edu/~vlsi/ECE559_Fall09/HW/HW6_Solution.pdf

- http://www.iosrjournals.org/iosr-jvlsi/papers/vol8-issue1/Version-1/E0801014346.pdf

- https://en.wikipedia.org/wiki/Sense_amplifier